- 上一篇:ARM7基于嵌入式系统的DMA传送方式研究

- 下一篇:HFSS有源小型化导航天线设计研究

数据采集的任务,具体地说,就是采集传感器输出的模拟信号并转换成计算机能识别的数字信号,然后送入计算机或相应的信号处理系统,根据不同需要进行相应的计算和处理,得出所需的数据。与此同时,将计算机得到的数据进行显示或打印,以便实现对某些物理量的监视,其中一部分数据还将被控制生产过程中的计算机控制系统用来控制某些物理量。数据采集几乎无孔不入,它已渗透到了地质、医药器械、雷达、通讯、遥感遥测等各个领域,为我们更好的获取信息提供了良好的基础。

另外,我们在评估一个信号源的质量时,也可以通过数据采集的手段将信号采集存入计算机,再通过各种处理方式来评价该信号源的好坏。这时,该数据采集系统就类似一台测试仪器。当然,我们需要确定系统的各项指标满足要求。

数据采集系统的性能好坏,主要取决于它的精度和速度。精度是通过有效位数来反映的,有效位数越高,要求系统的噪声就越低。速度是通过采样率来反映的,速度太高,传统的TIL逻辑常常不能满足需求,一般高速采集芯片的输出逻辑都为ECL逻辑。这样相应地增加了功耗。所以,在高速数据采集芯片的设计上是用大功耗来换取高速度,同时也减小了逻辑摆幅。根据目前芯片市场来看,高性能的A/D芯片己经达到了上GHZ的采样率。

1.2 国内外研究情况与发展趋势

2 FPGA数据采集系统架构

数据采集系统就是采集目标信号、对其进行存储并处理,转换成计算机可以识别的数据格式,并且最终依据需要进行不同数据形式的输出的系统。本设计中的高速图像采集处理系统需要同时以下特点:易于控制、具有高速图像处理能力、延时小等。

FPGA主要用于控制整个系统协调工作。作为数据采集系统的控制器,主要负责控制A/D工作转换控制、作为数据处理、数据采集系统的缓冲存储器等。由于系统中的核心逻辑功能均由FPGA来实现,可知本系统对FPGA的要求比较严格。综合考虑芯片性能和成本,选用Altera公司的新一代低成本FPGA—CycloneIII系列EP3C25F256I7芯片,Cyclone III FPGA是基于StratixⅡ的90 nm工艺推出的低成本FPGA。其在Cyclone的基础上增加了硬的DSP块,最大的Cyclone III规模是Cyclone的3倍,在芯片总体性能上要优于Cyclone系列器件。

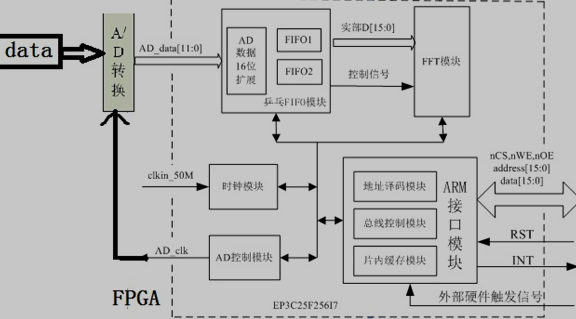

图2.1 FPGA数据采集系统架构图

图2.1是本系统中 内部功能模块的架构图。根据实现功能和外部硬件连接,在 内部实现乒乓 模块、 模块、时钟模块和 控制模块。下面将具体介绍各模块的功能、设计思路、实现过程与仿真结果。

本系统的设计思路是:信息通过AD9220芯片转换成12位的AD数据,再进入乒乓FIFO模块,扩展成16位的AD数据进行乒乓FIFO的数据缓存。再由FFT模块进行数据的计算处理。各模块的工作时序皆由FPGesxA控制。

3 时钟模块

3.1 FPGA中的时钟设计概述

时钟可以比喻成数字逻辑中的血液,几乎所有的信号都需要依靠时钟来向前传递。因此,时钟管理的重要性不言而喻。没有稳定、纯净的时钟作保障,再强大的数字芯片也无法完全发挥其功能。在FPGA的逻辑设计中,对于时钟域的设计是至关重要的。每个独立时钟域中时钟的走线排布、复位使能控制、时序约束以及多个时钟域之间的隔离处理,都将直接决定设计的功能及性能指标。下面将简单介绍一下在FPGA时钟设计中的几个重要概念。

(1)时钟偏移(Skew):

-

基于差分进化算法的自动...

-

基于混沌的图像加密通信...

-

Socket车位锁控制系统的服务器端设计实现

-

MATLAB基于时频分析的穿墙呼吸检测算法研究

-

基于LTE的OFDM无线传输链路设计与仿真

-

基于OFDM的用户接入控制技术研究

-

基于OFDM的数字图像无线传输关键技术研究

杂拟谷盗体内共生菌沃尔...

大众媒体对公共政策制定的影响

当代大学生慈善意识研究+文献综述

河岸冲刷和泥沙淤积的监测国内外研究现状

十二层带中心支撑钢结构...

乳业同业并购式全产业链...

酸性水汽提装置总汽提塔设计+CAD图纸

java+mysql车辆管理系统的设计+源代码

电站锅炉暖风器设计任务书

中考体育项目与体育教学合理结合的研究