- 上一篇:基于arm的卫星报警检测仪硬件设计

- 下一篇:高功率微波效应对接收机前门耦合器件研究

本文首先介绍了FPGA在当前背景下的发展情况和FPGA实现的功能和实现成本。然后介绍了UART的定义和UART协议的内容,课题要求采用RS-232协议,介绍了RS-232协议的要求。本文从模块功能分析入手,对课题要求进行流程图分析和模块编写。同时,对编写子模块进行测试、分析、调试。最后由顶层模块声明所有子模块端口并实例化子模块,最终集成UART串口功能。

全文共分五章,文章安排如下:

第一章为引言部分,主要介绍了课题背景和国内外研究现状以及文章组织安排。

第二章为设计思想部分,主要介绍了课题设计的方案并进行论证,简介了课题的设计思想和涉及相关技术以及相关技术的功能要求。

第三章为工作原理部分,主要从模块分析入手,对每个模块的设计思想和设计方法进行了介绍及分析。并且将模块集成器件原理图,介绍了相关重要代码。

第四章为顶层模块与测试部分,主要介绍了顶层模块将所有子模块集成及实例化的方法和设计。对各个子模块的测试结果进行分析并且分析整个课题的测试结果。

最终,对课题做了总结分析,并且提出了设计的不足和发展前景。

2. UART设计方法

2.1 UART协议背景

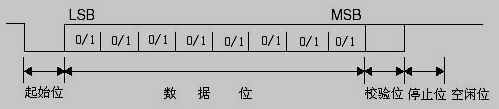

UART(Universal Asynchronous Receiver/Transmitter)即通用异步收发传输器。UART 协议作为一种低速通信协议,广泛应用于通信领域等各种场合。UART 基本可分为并口通信及串口通信两种。异步串口通信协议,工作原理是将传输数据的每个字符以串行方式一位接一位的传输。[10]图2.1 给出了其工作模式:

图2.1 UART工作原理

起始位:先发出一个逻辑“0”的信号,表示传输字符的开始。

数据位:紧跟起始位之后。数据位的个数可以是4、5、6、7、8等,构成一个字符,通常采用ASCII 码。从最低位开始传送,靠时钟来定位。

奇偶校验位:数据位加上这一位后(跟在数据位尾部),使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验数据传送的正确性。

停止位:它是一个字符数据的结束标志。可以是1 位、1.5 位、2 位的高电平(逻辑“1”)。

空闲位:处于逻辑“1”状态,表示当前线路上没有数据的传送。

波特率:是衡量数据传输速率的指针。表示为每秒钟传送的二进制位数(bit 数)。

本课题一帧10位(第一位为起始位,低电平),由1位起始位,8位数据位,1位奇偶校验位,1位停止位构成。采用9600的波特率,将系统时钟设为默认50MHZ。[1]

2.2 UART设计过程来.自/751论|文-网www.751com.cn/

UART主要分两个过程,接收过程和发送过程。接收过程是指信号检测器检测到RS-232总线上的数据,顺序读取串行数据并将其输出到CPU的过程。发送过程就是在波特率时钟下依次将加载的数据发送到RS-232发送端TxD,这样便产生了数据发送时序,然而发送过程需要实现并行-串行的转换,在发送步骤前需要将发送数据加载到发送前的移位寄存器内,再由移位寄存器一位一位进行发送。发送的时钟需要按照波特率时钟,设计要求需要波特率发生器模块。这里采用有限状态机(FSM)来描述UART核心控制逻辑方法,将其核心功能集成,使整个设计更加稳定可靠

-

Socket车位锁控制系统的服务器端设计实现

-

LSSVM采用几何方法的图像观测技术实现

-

Matlab数字下变频器的FPGA实现

-

CC2530物联网实验综合平台的设计与实现

-

基于EDA技术的FSK调制器设计与实现

-

Matlab图像纹理特征提取与实现

-

基于SUSAN角点检测算法研究与实现

大众媒体对公共政策制定的影响

杂拟谷盗体内共生菌沃尔...

中考体育项目与体育教学合理结合的研究

河岸冲刷和泥沙淤积的监测国内外研究现状

java+mysql车辆管理系统的设计+源代码

十二层带中心支撑钢结构...

酸性水汽提装置总汽提塔设计+CAD图纸

电站锅炉暖风器设计任务书

乳业同业并购式全产业链...

当代大学生慈善意识研究+文献综述