-

21

- 上一篇:进行伪码调相与线性调频复合探测信号参数提取方法研究

- 下一篇:四波剪切波长探测实验研究

4.4 低通滤波器设计 22

4.5 AD9854与AT89S52的接口 22

4.6 本章小结 24

5 DDS的软件设计 25

5.1 主程序流程图设计 25

5.2 信号产生的软件设计 25

5.3 本章小结 27

6 系统的仿真及数据分析 28

6.1 ADIsimDDS仿真软件介绍 28

6.2 仿真数据分析 28

6.3 本章小结 34

结 论 35

致 谢 37

参考文献 38

1 引言

人们所说的DDS(Direct Digital Synthesis)是20世纪70年代迅速发展起来的又一种新颖的频率合成技术。随着电子工程领域的实际需求,以及数字集成电路和微电子技术的发展,DDS技术日渐展露出它的优越性。

1.1 频率合成技术的发展概述

频率合成的理论成型于20世纪30年代,距今已有70多年的历史。随着这些年的迅速发展,逐步形成了目前的四种技术:直接频率合成技术,间接频率合成技术,直接数字式频率合成技术和混合式频率合成技术[31]。

1.1.1 直接频率合成技术

直接频率合成(direct frequency synthesis)技术是一种早期的信号合成方法。它通过混频器、倍频器、分频器对参考频率进行加、减、乘、除运算从而组合出所需要的频率信号。该方法产生的波形信号,相位噪声小,频率转换时间短,但同样存在很多缺憾。直接频率合成器设备相对复杂笨重,成本及功耗也大,同时会产生多种杂散分量和失真。

1.1.2 间接频率合成技术

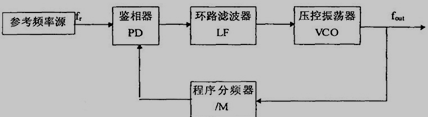

在此后出现了间接频率合成(indirect frequency synthesis)技术,又称之为锁相环(phase locked loop,PLL)频率合成技术,包括最先出现的模拟锁相环以及之后陆续出现的数字式锁相环和数模混合式锁相环。锁相环大多包含鉴相器(phase detector,PD)、环路滤波器、压控振荡器(voltage controlled oscillator,VCO)和分频器,其组成结构如图1.1所示。该方法利用环路的相位反馈控制原理来产生稳定的频率信号,并且由于具有良好的窄带跟踪滤波特性和杂散抑制能力,从而节省了大量滤波器以便于小型化和集成化。但锁相频率合成技术的频率转换时间相对而言比较长,是该方法存在的最大缺憾。

图1.1 锁相环结构图

1.1.3 直接数字频率合成技术

随着数字集成电路和微电子技术的迅猛发展,直接数字频率合成(direct digital frequency synthesis,DDS)技术随之诞生了。1971年3月,J.Tierney和C.M.Tader等人首先提出了DDS的概念[32]:利用数字方式累加相位,再以相位之和作为地址来查询正弦函数表得到正弦波幅度的离散数字序列,最后经D/A变换得到模拟正弦波输出。直接数字频率合成器主要由相位累加器、波形存储器、数模转换器和低通滤波器这些部分组成。直接数字频率合成器具有如下诸多优点[18]:

(1)输出频率相对带宽较宽,输出频率带宽的理论值可达50% ,但是考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际的输出频率带宽仍能达到40% ;

-

数字化钢轨精细打磨装备4G无线通信系统设计

-

基于OFDM的数字图像无线传输关键技术研究

-

matlab数字测频算法的仿真和研究

-

Matlab数字下变频器的FPGA实现

-

FPGA数字视频信息叠加软件设计+程序

-

基于DSP的数字锁相放大器设计

-

FPGA数字变频器的设计与仿真

当代大学生慈善意识研究+文献综述

河岸冲刷和泥沙淤积的监测国内外研究现状

大众媒体对公共政策制定的影响

java+mysql车辆管理系统的设计+源代码

杂拟谷盗体内共生菌沃尔...

酸性水汽提装置总汽提塔设计+CAD图纸

中考体育项目与体育教学合理结合的研究

十二层带中心支撑钢结构...

电站锅炉暖风器设计任务书

乳业同业并购式全产业链...