- 上一篇:MEMS传感器的发展与应用

- 下一篇:Windows环境下通信系统中压缩编码及解压缩译码软件设计

带通采样定理描述如下:设一个带限信号x(t),其频带限制在(fL,fH)内,如果其采样速率fS满足:

其中n为整数,取值区间为 ,N为 的整数部分。则采样后的信号的频谱不会发生混叠,即可以利用采样后的信号无失真地恢复得到原信号。

2.1.2数字下变频(DDC)原理

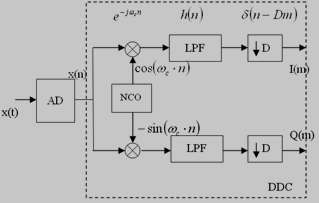

数字下变频器(DDC)由数控振荡器(NCO)、混频器、低通滤波器(LPF)和抽取器组成,如图2.1所示。数控振荡器(NCO)产生角频率为 ( )的两路正交信号 和 ,与AD采样得到的数据混频,得到复信号 ,将混频后的信号通过低通滤波器(LPF)滤波,再进行抽取,最后得到所需的基带信号 ,以满足后续处理器对数据率的要求。经过数字下变频处理后的信号的数学表达式如式(2.2)所示。

图2.1 数字下变频原理示意图

抽取倍数越高,要求的滤波器阶数就越高。然而受器件资源的限制,当滤波器阶数非常高时,实现图2.1中所示的单级抽取结构是非常困难的。但是,可以通过多级抽取的方法来降低对滤波器阶数的要求,从而实现高倍抽取。多级滤波抽取结构总的抽取率是各级抽取率的乘积。

2.2 直接数字频率合成(DDS)原理

DDS的基本结构主要有相位累加器、相位调制器、正弦波数据表(ROM)、D/A转换器等构成。其原理图如2.2所示,预先在波形存储器(ROM)中存入所要求产生的波形的抽样值(二进制编码)。在参考时钟 clock 的控制下,相位累加器对频率控制字fword进行线性累加,再与相位字pword相加得到相位码 。将每次得到的相位码 作为相位取样地址对波形存储器(ROM)寻址,得到离散的幅度编码,经过 D/A 转换器将数字信号转换成模拟信号输出。文献综述

相位累加器的位数应该不小于ROM地址的位数,当相位累加器的位数等于ROM的地址位数时,直接将累加器的输出作为ROM地址就可以了;当累加器的位数大于ROM地址位数时,应该按ROM地址位数从累加器输出中按高位到低位的顺序截取相应的位数作为ROM的地址。当相位累加器加满量时就会产生一次溢出,这样就完成了一个周期,这个周期也就是DDS输出信号的一个周期。那么可得输出频率:

(2.3)

其中N为累加器位数,B为频率控制字fword, 为系统时钟。由此可知,改变波形存储器(ROM)内容可以改变输出波形类型,改变频率字fword和参考时钟clock可以改变输出信号频率,而改变相位字pword可以改变输出波形初始相位

-

基于差分进化算法的自动...

-

HFSS的Vivaldi天线的仿真设计

-

AT89C52单片机基于max038的信号发生器设计+程序

-

微波小信号放大器的设计ADS仿真

-

STC89C52单片机MAX038的程控信...

-

C波段宽带均衡器设计

-

心音信息传感器电路设计及其信号处理

乳业同业并购式全产业链...

杂拟谷盗体内共生菌沃尔...

电站锅炉暖风器设计任务书

酸性水汽提装置总汽提塔设计+CAD图纸

大众媒体对公共政策制定的影响

中考体育项目与体育教学合理结合的研究

java+mysql车辆管理系统的设计+源代码

十二层带中心支撑钢结构...

当代大学生慈善意识研究+文献综述

河岸冲刷和泥沙淤积的监测国内外研究现状